# HEWLETT-PACKARD

**OCTOBER 1984**

# HEWLETT-PACKARD JOURNAL

October 1984 Volume 35 • Number 10

#### **Contents**

The HP 3065 Board Test Family: A System Overview, by Thomas R. Fay and John E. McDermid A "computer behind the pins" design, friendly data entry, test safeguards, and a built-in device test library are some of the features.

- 6 HP Q-STAR

- 9 Confirmation-Diagnostics

1 Authors

Automatic Test Program Generation for Digital Board Testing, by Robert E. Balliew

The user is freed from having to assign test inputs and outputs and define test patterns

for most devices.

13 Board Test Connection Terminology

Digital Subsystem for a Board Test System, by Matthew L. Snook and Michael A. Teska A keep/toggle vector definition scheme reduces storage requirements and increases test throughput.

- 16 Digital Test Throughput

- Safeguarding Devices Against Stress Caused by In-Circuit Testing, by Vance R. Harwood Built-in software takes care of this for the HP 3065 user.

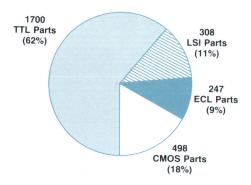

- **Extensive Library Simplifies Digital Board Test Setup,** by Randy W. Holmberg Test routines for over 2700 common digital devices are part of the HP 3065 software.

- 25 An Interpreter-Based Board Test Programming Environment, by Mark A. Mathieu This high-level language extends BASIC for use in defining circuit board tests.

- **Testing for Short-Circuit Failures, by T. Michael Hendricks** One has to separate random short-circuits from desired short-circuits and watch out for "phantoms."

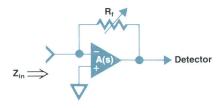

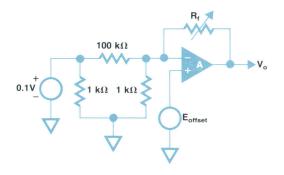

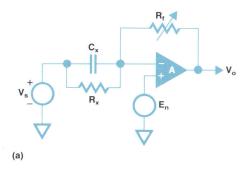

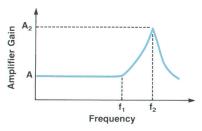

- Reducing Errors in Automated Analog In-Circuit Test Generation, by John E. McDermid Careful design is required to generate correct tests for more than 90% of a board's components.

Editor, Richard P. Dolan • Associate Editor, Kenneth A. Shaw • Art Director, Photographer, Arvid A. Danielson • Illustrators, Nancy S. Vanderbloom, Susan E. Wright • European Production Supervisor, Michael Zandwijken • Publisher, Russell M. H. Berg

#### In this Issue

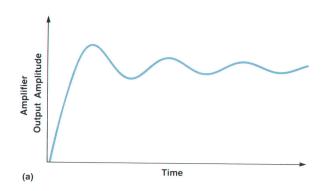

If our designs and our manufacturing processes were perfect, there would be no need for testing, since every product coming off the assembly line would work perfectly. In reality, the more complex the product, the more testing it needs, and the more difficult the task of developing thorough, exhaustive tests that can be completed in a reasonable amount of time. In electronic printed circuit board production, automatic test equipment can be considered a contribution to the state of the art if it tests larger, more complex boards, tests them faster, tests them more thoroughly, tests them more safely, and/or makes it easier for the test programmer to generate tests. In

this issue, the designers of the HP 3065 Board Test System tell us how their system makes contributions in all of these ways. Designed for high-volume production testing of large, complex printed circuit boards, the HP 3065 does both functional testing (Does the board work?) and in-circuit testing (Is any part wrong, misloaded, faulty, or out of tolerance? Are there solder splashes causing short circuits? Is there assembly damage?). By carefully minimizing the biggest contributor to test time—the long overhead time between individual tests while the computer transfers data—the HP 3065's designers have made the system fast, particularly in testing integrated circuits on boards. It can test more than 30 ICs per second of just about any complexity. In 20 seconds, it can test for short circuits and test all of the analog and digital parts on a 14-by-18-inch board with 206 ICs and 100 analog devices.

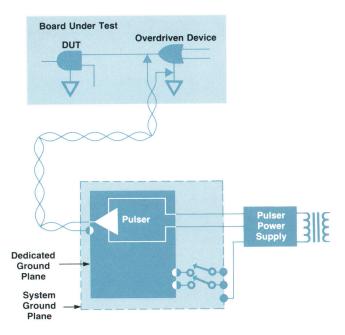

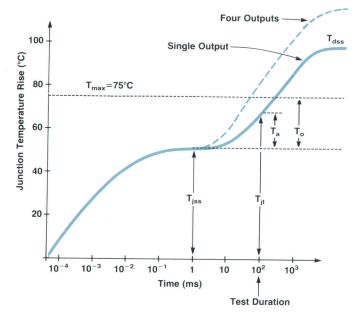

The HP 3065 does in-circuit testing by forcing the inputs of a device to known levels. To do this, it sometimes has to overpower other devices on the board that are connected to the device under test. This technique, which is called overdriving, has been known to cause failures at times and has been suspected of shortening the lifetimes of circuit components. So that this won't be a problem in the HP 3065, the system's software automatically analyzes each test for damage potential and limits currents, voltages, and test durations to safe values. The article on page 20 describes how these safe levels are determined and maintained.

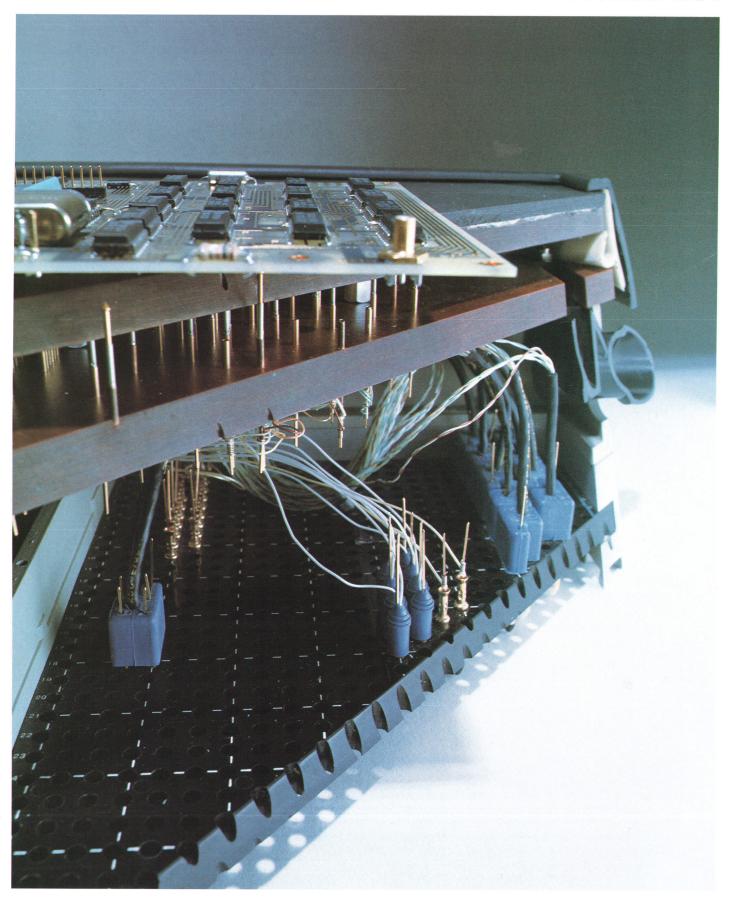

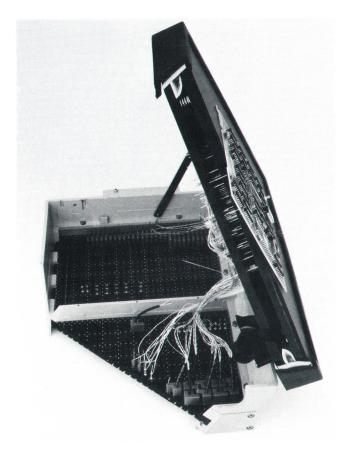

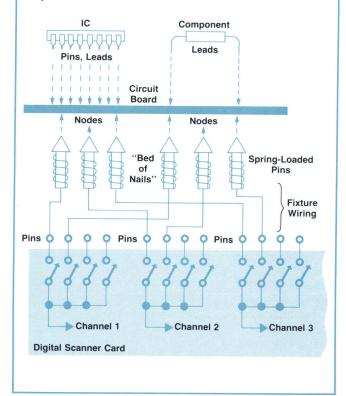

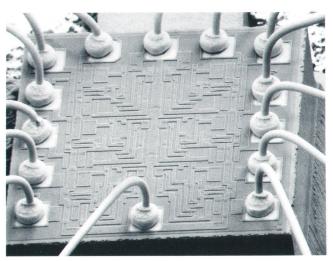

Like many other board test systems, the HP 3065 uses a bed-of-nails test fixture. Our cover photograph shows it cut in half so you can see what's inside. The board under test is placed on top and then a vacuum is applied (through the hoses you can see in the picture) to pull the platform holding the board down towards the platform underneath it. This forces the pins of the test fixture against the nodes of the printed circuit board. To write a test program for a particular board, all a programmer has to do is tell the HP 3065 what kinds of components are connected to the various nodes. If the board has been designed using a CAD (computer-aided design) system, the HP 3065 can simply be given a data file from the CAD system. The HP 3065 then looks in its large library for individual component tests, writes an overall test program, optimizes it, and generates a wiring diagram to tell the test personnel how to connect the bed of nails to the system's pins (they're in the holes in the bottom platform in the cover photo). If there are components on the board that aren't in the system's library, the programmer has to tell the system how to test them. Usually, 90% or more of the components will be in the library. Three articles in this issue deal with various facets of the HP 3065's automatic test generation software.

High-volume testers for complex boards aren't inexpensive. However, the HP 3065's high throughput and automatic test generation tend to minimize the cost per test, and the information it gathers about production defects can lead to improvement of the design and the manufacturing process. All things considered, it can be the most cost-effective solution to a formidable problem.

-R. P. Dolan

#### What's Ahead

The November issue will describe the design and features of three different kinds of HP products. An easy-to-use network analyzer, the HP 3577A, and a companion S-parameter test set, the HP 35677A/B, are discussed in three articles. Two more articles describe the HP 293X family of high-quality dot-matrix impact printers and the custom IC developed to coordinate their printing functions. The last article describes a rugged terminal, the HP 3081A, designed for use in severe industrial environments.

## The HP 3065 Board Test Family: A System Overview

This board test system features menu-driven automatic test generation, high digital IC throughput, overdrive protection, multiple test stations, and networking capability.

#### by Thomas R. Fay and John E. McDermid

HE MANUFACTURE OF TODAY's sophisticated electronic equipment usually requires the assembly of one or more printed circuit boards, each containing one or more integrated circuits and a number of discrete components. As these boards grow more complex, increasing in the number of components and interconnections, the need for testing these boards quickly and easily becomes more important. The sheer numbers of parts and subassemblies conspire to make maintaining quality and production yields difficult. What is worse, the farther along in assembly a product gets, the more difficult it becomes to excite, detect, and diagnose manufacturing defects. The result is that it becomes very attractive to test subassemblies at a level of integration high enough so that the number of remaining assembly steps is manageable, but before the view into the causes of problems becomes clouded by complexity. Printed circuit boards fit this bill nicely—not too complex to test, diagnose, and repair; not so low-level that the number of boards to be assembled presents a severe quality problem.

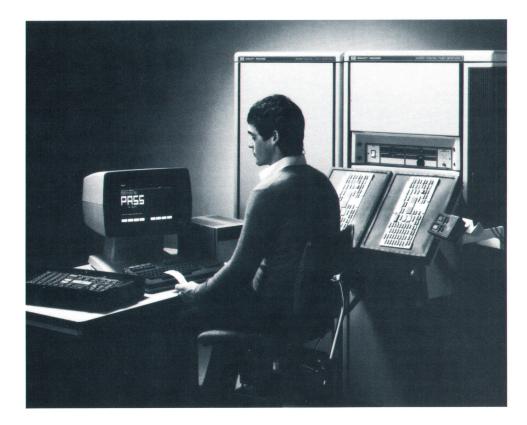

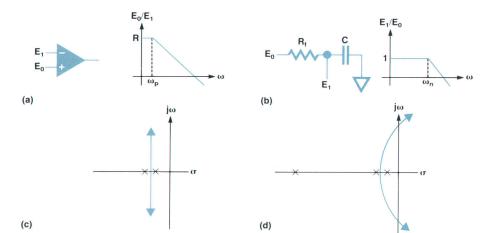

The HP 3065 Board Test System (Fig. 1) is Hewlett-Packard's latest model for evaluating complex analog/digital printed circuit boards. Building on the strengths of HP's earlier board test systems, it has many features that simplify the development of complex board tests and enhance their usefulness in the production environment. A "computer behind the pins" design incorporates an improved in-circuit test program generator, called IPG-II, that is capable of generating correct tests for an average of 90% of the circuit components and digital devices found on a typical circuit board. Up to 22 analog or digital cards may be used in the system. Each digital card can address up to 48 circuit nodes and each analog card can address up to 64 nodes. The wiring connections between the cards and the board are assigned by IPG-II, because the digital cards multiplex one driver/receiver channel for every four nodes (12 chan-

Fig. 1. The HP 3065 Board Test Family provides printed circuit board manufacturers with a combination of high throughput, excellent test quality, and low programming costs for evaluating complex digital and analog circuit boards. The basic configuration shown consists of a measurement section (right), an instrument section (center), and a programming station (left).

nels per card). The multiplexing scheme lowers hardware cost and the wiring assignment by IPG-II reduces test setup time.

Because the HP 3065 can perform both analog and digital tests at both the in-circuit device and the board function level, complex ICs and circuits such as ROMs, microprocessors, analog-to-digital converters, memory boards, and instrumentation amplifiers can be evaluated.

In-circuit testing of digital devices often requires overdriving adjacent device inputs and outputs to obtain the necessary test conditions. To minimize any stress on these overdriven devices that might degrade their functionality or lifetime, the HP 3065 has carefully designed safeguards built into its test software.

Careful attention to the HP 3065's hardware and software design has resulted in improved test throughput of greater than 30 ICs per second. A friendly forms entry format allows nontechnical personnel to enter board descriptions quickly to lower the cost of test development. Alternatively, the board description can be supplied directly in ASCII format by the CAD/CAM system used to design the board.

Since the data gathered during production testing is often of value to other manufacturing activities such as quality control, inventory control, and yield improvement, the HP 3065 supports several links for networking to other systems, including earlier HP 306X Test Systems, HP 1000 and HP 3000 Computers, and many HP desktop computers. The box on page 6 describes the HP Q-STAR features recently added to the HP 3065.

#### **Board Testing Considerations**

There are several important reasons for using a board test system. Most frequently it is used to filter the manufacturing process so that defects can be detected and eliminated at the earliest possible stage of the process. Early detection reduces the expense associated with correcting these defects.

A second and very important reason is to measure the manufacturing process so that corrective action can be taken to prevent future defects. An HP 3065 System allows parameters to be measured on every component on the printed circuit board as well as the board itself. With this kind of measurement capability, large amounts of data can be taken and examined, control charts developed, and the effect of process changes determined.

A third reason is to increase the capacity of an existing production process. Often, the ability to increase the volume of boards manufactured in a given time is limited by the availability of skilled technicians. If much of their time is spent tracking difficult problems that in the end can be traced to short-circuited, misloaded, wrong, or grossly defective components, then throughput can be greatly improved with the use of a board test system.

The major application area for the HP 3065 is in the production environment. While this system can be used in field or depot repair applications, the necessary quantity of test fixtures is typically larger and the quantity of boards of a single type is lower. Hence, for some field repair applications, the system may not be cost-effective. Also many of the library tests are customized to the type of fault spectrum that is found in production. As an example, on-board

short circuits are seldom the cause of a field failure, but can be quite common in the production environment.

Production testing of printed circuit boards has some rather strong constraints. First, the development of tests for boards naturally must follow the development of those boards and hence occurs near the end of the development cycle. On the other hand, testing is a vital part of starting up production of the boards, especially in the beginning when the production process needs to be fine-tuned. The result is a squeeze play on the test development time and the test programmer, especially since products often contain multiple boards that reach production almost simultaneously. In these boom situations, the number of skilled test designers frequently falls short of the requirements, and is often too small in any case.

Another severe constraint is the way that testing fits into the manufacturing process. First, it must not take much time out of the total manufacturing time for a board, or it becomes a bottleneck and a work-in-process inventory builder—neither very desirable. Second, it must test the boards thoroughly so that what emerges from the test process are reliable boards. And third, it must provide diagnostic information so that defective boards can be quickly repaired. Finally, testing must provide useful real-time feedback on the manufacturing process so that production yields can be steadily improved and excess scrap can be avoided. Being able to communicate test results to other manufacturing computer data bases and systems is also important.

The HP 3065 Board Test System deals with all of these problems. Its internal test program generator (IPG-II) automatically generates test sequences from a description of the board so that tests that cover 90% of the manufacturing defects can be created very rapidly. These tests can be used to provide early feedback on board quality and can be further enhanced manually as time permits to increase coverage and further improve yields. The automated nature of the test generation and the simplified user interface combine to allow novice technicians to handle the testing. The use of a multiprogrammed computer as a controller allows the HP 3065 to support multiple programming stations to meet widely varying test development work loads. The same computer has sufficient power to let the HP 3065 support up to three test heads, each providing excellent test throughput.

Within the frequency limitation of the bed of nails (matrix of spring-loaded pins for making connections to the board under test, see cover photograph) and the accuracy limits of the HP 3065, the system is also capable of performing functional testing on the board under test. The full range of HP's programmable HP-IB (IEEE 488) instrumentation can be used to facilitate these measurements. This makes it possible to test individual components and functionally check, adjust, and qualify a printed circuit board with one operation on the same piece of test equipment.

#### **System Hardware**

The HP 3065 System is the culmination of two significant development efforts—one in hardware, the other in software. The hardware effort produced about 29 different printed circuit boards (some of which are quite large) and three full bays

of equipment. This hardware has three major components: the controller, the test heads and optional test-head equipment, and the programming stations and peripheral devices. Controller. The HP 3065C Controller is an HP 1000 E-Series Computer with up to 2M bytes of memory, a 140M-byte disc drive, and a quick-disconnect panel for test heads, programming stations, and peripherals. The controller is capable of concurrently operating up to three test heads and three programming stations. The test heads and the programming stations can be located up to 90 meters away from the controller by adding two bus extenders to the controller for each remote test station. Up to six extenders can be mounted in the controller. Network interfaces are provided for both high-level data link control (HDLC) and X.25 protocols. HP-IB interfaces are a standard part of the system. Additionally, a modem interface is provided for a remote terminal that can be used as either a programming station or for remote diagnostic capability.

**Test Heads.** A test head consists of two full bays: the measurement bay and the instrument bay. Within the measure-

### **HP Q-STAR**

The HP 3065 is more than just a board test system, it is a cornerstone of the HP Q-STAR (Quality Systems for Test, Analysis, and Repair) network. This integrated package of software and hardware is designed to simplify the solution of interrelated problems of test, analysis, and repair of printed circuit boards. Some of the features provided by HP Q-STAR include:

- HP CAD-VANTAGE. This software allows users to develop test programs faster by automatically capturing circuit data from a wide variety of commercially available or proprietary CAD systems.

- HP Q-STATS. This software can be used to identify trends in component parameters, manufacturing board yields, repair productivity, and quality by providing test managers and programmers with summarized data from the test and repair processes.

- HP CHEKPOINT. This software automatically verifies that the spring-loaded pins in the bed-of-nails board test fixture are actually making contact to the board under test.

- HP REMOTE SUPPORT/3065. This feature provides on-line communications between HP 3065 computer systems and HP support centers to help reduce downtime when servicing is required.

- High-level network access. This software allows users to share data among various computer systems via RS-232-C/V.24, HP-IB (IEEE 488), and HP-DS links.

- Expanded digital test library. New in-circuit tests for the most popular new LSI devices to help reduce test development time for state-of-the-art board designs.

- IPG-II enhancements. New analysis algorithms reduce the amount of manual adjustments required to complete development of a test program.

- Bar-code data entry. The HP 3065 software now allows the use of a bar-code reader for high-level entry of repair and board identification data for tracking boards through the test and repair loop.

- HP PAPERLESS REPAIR/REPORTING. This software eliminates the need for paper failure reports, permits tracking of the test and repair history for improved repair operation control, and gathers the repair data for analysis by HP Q-STATS.

ment bay are floating voltage and current sources. In addition to dc, ac, and function generator sources, there are ac and dc voltmeters, frequency counters, and a pulse width detector. These sources and detectors can be used with special circuitry to isolate the component under test and measure other parameters such as resistance, capacitance, inductance, diode voltage drop, and transistor ac  $\beta$ . Also within the measurement bay are digital drivers and receivers, memory for test vectors, and a high-speed computer to sequence and validate test vectors. All multiplexing necessary to interface to the board under test is contained in this bay. The instrument bay contains power supplies for the device under test and any optional HP-IB instrumentation that the user may wish to configure into the system. Additional equipment frequently requested for particular applications includes an HP 1980A/B Oscilloscope, an HP 3325A Frequency Synthesizer, an HP 5335A Universal Counter, and an HP 3456A System Voltmeter.

**Programming Stations.** Programming stations consist of terminals, additional computer memory, and whatever peripherals are desired. These programming stations can be used while the test head is in operation without significantly affecting test-head performance.

#### **System Software**

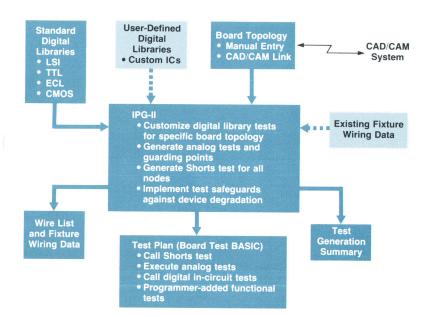

The software for the HP 3065 is the result of a large design effort—writing, integrating, and testing about 450,000 lines of source code. This software is a fully integrated system of eleven major packages (Fig. 2):

- Screen editor

- Board Test BASIC

- Manual board topology entry

- Board topology from computer-aided design and manufacturing systems

- Automatic in/circuit test program generator (IPG-II)

- Wire list

- Test plan

- Vector control language (VCL)

- Digital libraries and test safeguards

- Networking

- Confirmation and diagnostics.

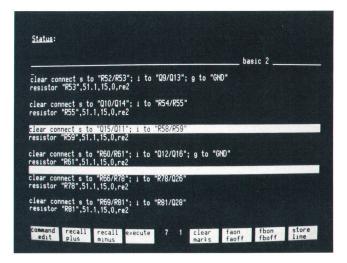

Screen Editor. A very important design objective was to integrate these software entities so that the user perceives only one. The key to this integration is the editor. It provides users with a window on the software that is always the same. At the top of the programming station's display screen is a status line where the current state of the machine and any error messages are displayed. The next line down is the command line. A statement in the command line is parsed and executed immediately when the execute softkey is pressed. Execution of statements on this line is independent of the editor's mode. When the command/edit softkey is pressed, the cursor toggles between the command line and the edit area. Files are placed in the edit area with a load command. Whenever editing is done, each line is checked for correct syntax before it is accepted. If an error is detected, it is reported in the status line so that the user can correct it immediately. The definition of what is syntactically correct changes with each mode.

**Board Test BASIC**. Board Test BASIC is an adaptation of BASIC to the board test environment. It has been written

so that language extensions can be provided for specific board test functions such as testing a resistor or a digital device. The interpretive nature of BASIC makes it easy to test and debug. Specialized statements such as test make invocation of high-speed compiled languages (like that used to test digital devices) very natural and remove the speed limitation often associated with an interpretive language. Board Test BASIC is the control structure for the user. Whether the task is sequencing a series of tests, copying a file from one location to another, or controlling a group of editor commands, it is accomplished through BASIC. See the article on page 25 for more details.

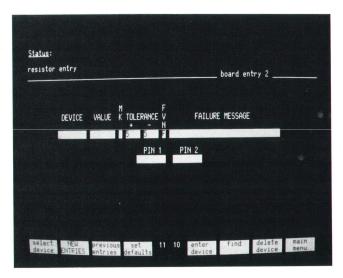

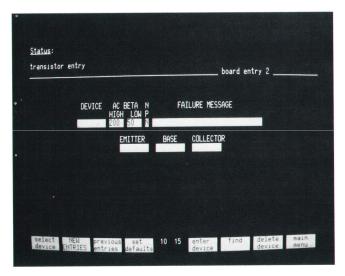

Manual Entry. The manual board topology entry is a special software product optimized for use by clerically skilled personnel. Its "fill-in-the-blank" forms entry is easy to learn and minimizes the amount of typing that needs to be done to enter data manually. Data for entry into this package is taken directly from the schematic and material list for the board. (Examples of displays for entering data for a resistor and a transistor are shown in Fig. 3 and Fig. 4.) This package can be entered either from the command line or scheduled from a BASIC program. Scheduling it from a program allows a user to predefine all files and output devices so that clerically skilled personnel will not need any programming knowledge.

CAD/CAM Entry. The board description entry software is designed to accept ASCII files (from any source) as an alternative way of obtaining information about the board. If material lists and board topology are available from another computer in ASCII form, this method of entry will greatly enhance the productivity of the system. When an ASCII file is available in the predefined format, it can be compiled into a file that can be viewed and edited on the HP 3065 using the board description package. This allows corrections to be made or information added in a straightforward way.

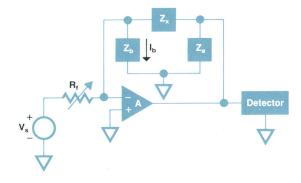

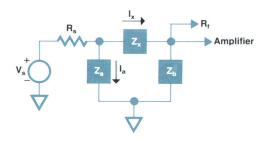

**IPG-II.** After the printed circuit board information is loaded, the next step is to develop a test program. An automatic in-circuit test program generator, called IPG-II, is

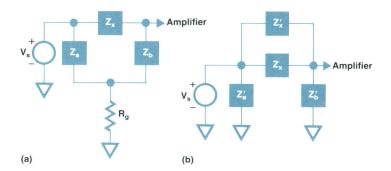

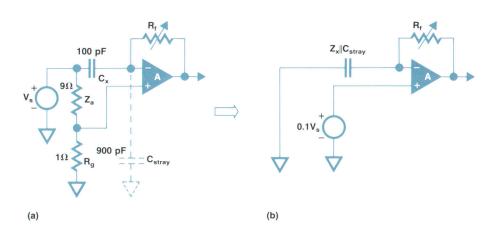

provided that produces analog and/or digital tests for each individual component. This analysis takes into account test instrumentation effects on the measurement process and reduces the effects of other devices connected to the component under test by using a technique called guarding. Automatic program generation uses the topology information from the board, material list information, and library information on digital parts and then combines them to produce a BASIC program called Test Plan. Experience has demonstrated that more than 90% of these tests will not require any manual adjustments by the user (see articles on page 11 and page 31).

Wire List. A second output of the program generator is a complete set of fixture wiring instructions and a wire list. Each type of board to be tested requires a specially designed text fixture (bed of nails) which uses spring-loaded pins to make connections to each critical circuit node on the board (see Fig. 5). The wire list is a file that specifies which test fixture connection points must be connected by the user to which spring-loaded pin. For convenience of production change orders, an old wire list can be used as an input to the program generator and a minimum set of changes will be output.

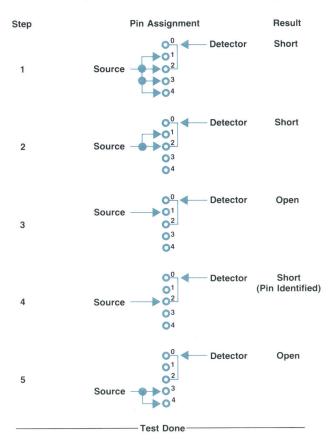

Test Plan. The Test Plan program output by the in-circuit program generator IPG-II serves to sequence all the tests for the board. It can be edited or augmented by the user in the same way as any BASIC program. Test Plan controls four major types of tests: the Shorts test, analog in-circuit tests, digital in-circuit tests, and functional tests. The Shorts test (see article on page 28) is designed to find connectivity errors on the board. It tests the connectivity from one node to all other nodes on the board and expects to find no undesired connections on a good board. Analog tests check passive and many active components for important parameters such as resistance, capacitance, and inductance. Digital tests apply test patterns to prove that the correct device is installed and that a connection exists to all pins.

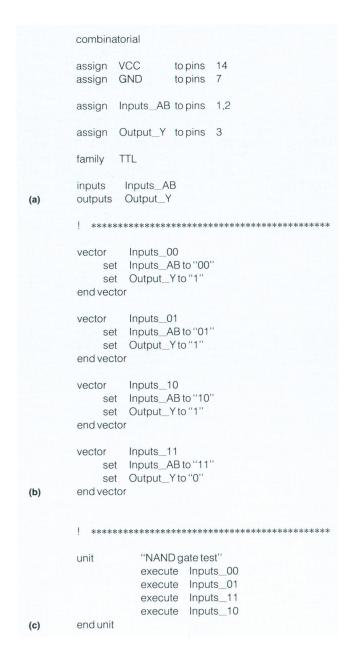

VCL and Digital Libraries. Digital tests are written in vector control language (VCL). This compiled language is de-

Fig. 2. The software system supplied with the HP 3065 Board Test System. IPG-II is HP's second-generation in-circuit test program generator. Requiring only board topology as its input, IPG-II uses digital test libraries and the circuit's description to generate the analog and digital in-circuit test program.

Fig. 3. Display screen for entering resistor test information.

signed explicitly for the bit-slice processor within the test head. The high-level language is compiled into object form and stored in a special disc file called the turbofile. When a digital test is executed, the object code for that particular device is retrieved from the disc (via the cache memory) and sent to the test head where it becomes the executable code for the bit-slice processor. Included in the digital device tests are safeguard features to protect devices under test from potential stress caused by in-circuit testing. These protective features and the primary failure mechanisms influencing their design in the HP 3065 are discussed in the article on page 20.

The architecture of the vector control language for a digital test closely parallels the architecture of the hardware. Structurally it is divided into three sections: the device declaration section, the vector definition section, and the vector execution section. Information in the device declaration section describes the device pins and their function, such as input, output, or bidirectional, and provides information on how to connect the device to drivers and receivers. The vector definition section describes the test vectors (device input/output conditions). It is this data that is stored in the pin RAMs. The vector execution section sequences the vectors, subroutines, homing loops, and counters, and forms the executable code for the bit-slice processor.

Networking. A very important feature of the system is the ability to interconnect several HP 3065 Systems. The network used is a topology-independent architecture supporting such diverse structures as star, string, and ring connections. Each network node has a store-and-forward capability and a network-wide nodal addressing system. A network system can be configured with redundant paths and a dynamic message rerouting system automatically bypasses a "down" node or communication link. The integrity of the message is assured by cyclic redundancy checking on all frames that are sent. The interface retransmits all frames received in error so that even large files can be received error free. The result is that a single copy statement in BASIC is all that is required to communicate with a

Fig. 4. Display screen for entering transistor test information.

remote device or file. The store-and-forward operation occurs transparently on intervening machines and does not affect testing.

Confirmation and Diagnostics. Finally, no system would be worthwhile if failures couldn't be detected and isolated

**Fig. 5.** Cutaway view of test fixture. Contact to the board under test is made by using vacuum to pull the board down onto a configuration of spring-loaded pins (bed of nails). The HP 3065 tells the user how to wire these pins to the test fixture.

### **Confirmation-Diagnostics**

Incorporated into an electronic production line, the HP 3065 Board Test System becomes a key factor in determining overall throughput. Therefore, system failures can have a tremendous impact on productivity. Because of this, the HP 3065 is provided with a hardware/software package that can quickly and accurately diagnose failing hardware in the system.

Confirmation-Diagnostics, as this package has become known, had several design objectives. The first was to provide a fast verification of system integrity. This is called confirmation. This test, which runs in less than 20 minutes, verifies that all system hardware is operating properly. This knowledge is very important to a production line supervisor who must be able to trust the board test results produced by the HP 3065.

The second objective of Confirmation-Diagnostics was to provide a set of tests that would be able to locate the exact hardware failure, should one be detected by the confirmation test. This software package will isolate a problem in the system by running more comprehensive tests. These tests are able to isolate a failure down to any single relay or to the electronics on any single printed circuit board. Thus, a failure can be isolated quickly down to a module that can be replaced easily in the field. This saves the customer costly down time.

Implementing Confirmation-Diagnostics was part of the overall product definition from the very beginning. Every printed circuit board designed for the system includes features that allow it to be tested functionally under remote software control. One printed circuit board in the scanner bay was designated specifically as a testing card. The electronics on this card interfaces to the other scanner cards through a special fixture. This test card-fixture combination allows diagnostic access to every scanner point in the system. The system DVM and other test hardware built into the HP 3065 System can use this access to verify all the electronics in the system.

The major investment in implementing Confirmation-Diagnostics was in software development. This portion of the project involved over five engineer-years of effort. The software package includes a menu-driven, easy-to-operate user interface that makes extensive use of softkeys. It also includes almost one thousand tests, each one designed to test particular system functions. These tests are executed and managed by an executive which also keeps a log of all tests performed. This executive also analyzes the test results to determine which module or modules are faulty.

Diagnostics can be run automatically on a complete HP 3065 System, or can be run selectively on any subsystem, printed circuit board, or even individual relays. In addition, any individual test can be run in a loop or single-stepped through its various operations. These features are useful for in-depth troubleshooting by field service personnel.

Randy W. Holmberg

Systems Engineer

Southern Sales Region

quickly. The confirmation and diagnostic packages are designed to do just that (see box). The confirmation part of the software is designed to be run by any board test operator. All that is required of the operator is to establish a valid log-on, place the diagnostic fixture on the system, and press **START**. Then, in ten to twenty minutes, depending on the hardware configuration, a test head can be certified functional. The pass/fail condition is returned to the operator. If the test head is inoperative, service-trained personnel should be consulted. By invoking the diagnostic package for the test head, service personnel can view failing confirmation tests.

An automatic diagnostic feature can be used to determine the most probable module to replace. Another important part of the diagnostic package is the ability to use it remotely. This allows HP service personnel to access a user's system from their office and come much better prepared to solve a problem in the field.

#### **Acknowledgments**

The design of the HP 3065 was a large and exciting effort. Many people made contributions to the development of this system. The electrical hardware was the result of the efforts made by G. Siva Bushanam, Al Gookin, Steve Greer, Bob Illick, John Ketchum, Steve List, Dave Potson, Ken Saller, Larry Smeins, Mike Teska, and Brian Wood.

The software and system design was done by Bob Balliew, Doug Baskins, Roy Broeren, Rod Browen, Martha Conant, Bud Cribar, Dave Crook, Dave Glasgow, Bill Groves, Vance Harwood, Mike Hendricks, Randy Holmberg, Doug Manley, Mark Matthieu, Ron Mathieson, Dave McGownd, and Ken Posse.

The mechanical design benefitted from the contributions of Jim Berry, Rod Harris, Jim Hayes, Jim Jones, Muriel Keller, Dave Marttinen, and Bill Smith.

We would also like to thank Cullen Darnell and John Scruggs for their continued support throughout the duration of the project.

#### Reference

1. D.T. Crook, "Analog In-Circuit Component Measurements: Problems and Solutions," *Hewlett-Packard Journal*, Vol. 30, no. 3, March 1979.

### **Authors**

October 1984

testing. Mike was born in Ann Arbor, Michigan and attended the University of Michigan, receiving a BSEE degree in 1979. He and his wife are advisors for a church youth group in Loveland, Colorado, where they and their new son make their home. When not sailing his Hobie Cat on nearby Boyd Lake, Mike enjoys backpacking, woodworking, and playing guitar.

gineer. He then transferred to the R&D lab to work on software for the HP 3065 Board Test System and now is a systems engineer for HP's Atlanta Sales Office. He has taught several courses on HP's circuit test products and is active in the Metropolitan Community Church of Atlanta. Randy enjoys swimming, hiking, and working on his new home in Marietta, Georgia.

#### 4 THP 3065 Board Test System T

#### Thomas R. Fay

Tom Fay studied mathematics at Kalamazoo College (BA 1971) and the University of Michigan (MS 1972) and computer science at San Jose State University (MS 1980). After working as a programmer for a major retail chain and then as a software develop-

ment manager for a major semiconductor manufacturer, he joined HP in 1979 as a software engineer. Tom worked on the MODCAL compiler, printed circuit design, and the software for the HP 3065's digital subsystem before assuming his current responsibility as project manager for HP 3065 test generation software. He is the author of two articles on software libraries and documentation and a member of the IEEE Computer Society and the ACM. Born in Decatur, Indiana, he now makes Fort Collins, Colorado his home. Tom is married and enjoys bicycling, swimming, tennis, and fishing.

#### John E. McDermid

Author's biography appears elsewhere in this section.

#### 11 \_\_\_ Automatic Digital Test Generation \_\_\_

#### Robert E. Balliew

Bob Balliew has contributed to the design of the ECL driver/comparator card for the HP DTS-70 Digital Test System, the design of the HP 3052A Data Acquisition System, and the production of the HP 3060A Circuit Test System since he began work at HP in 1977.

A graduate of Colorado State University (BSEE 1977), he was born in Denver, Colorado. Bob lives in Loveland, Colorado, is married (his wife is an HP marketing engineer), and has one child. Outside of work, he enjoys working on his house and yard when not hiking or skiing.

#### 14 \_\_\_ Digital Board Test Subsystem \_\_\_

#### Michael A. Teska

A project manager for enhancements to the HP 3065 Board Test System, Mike Teska also designed the pin electronics for the HP 3065. With HP since 1979, his work has resulted in a patent application related to reducing potential damage caused by in-circuit

#### Matthew L. Snook

Involved with both R&D and production for the HP 3065 Board Test System, Matt Snook has been with HP since 1979. His contributions have resulted in two patent applications and one conference paper related to circuit board testing. Born in Mexico, Mis-

souri, Matt attended the University of Missouri at Rolla, earning a BSEE degree in 1979. He lives in Loveland, Colorado and has many interests—modern music and dancing, skiing, scuba diving, camping, boardsailing, motorcycling, and travel.

#### 20 \_\_ In-Circuit Test Safeguards \_\_

#### Vance R. Harwood

Interested in data security and software design methodologies, Vance Harwood is an R&D manager at HP's Manufacturing Test Division in Loveland, Colorado. He holds a BSEE degree (1975) from the University of Colorado and has done graduate work in

computer science and electrical engineering at Arizona State University. Before coming to HP in 1979, Vance worked on high-speed digital communications design and microprocessor-based controllers and instrumentation for two major defense contractors. At HP he has done software and hardware design for the HP 3065 Board Test System and its predecessor, the HP 3060. Vance is a member of the IEEE, was born in Denver, Colorado, and is active in church functions. He lives in Loveland, Colorado, is married and the father of two children, and is interested in skiing, tennis, and science fiction.

#### 23 = Digital Test Library =

#### Randy W. Holmberg

Born in Los Alamos, New Mexico, Randy Holmberg studied electrical engineering at Colorado State University (BSEE 1978). After a year of graduate work in computer engineering at Purdue University, he joined HP in 1979 as a circuit test marketing en-

#### 25 = Board Test BASIC ===

#### Mark A. Mathieu

A native of the upper peninsula of Michigan, Mark Mathieu studied computer science (BSCS 1979) at Michigan Technological University. After working for nearly two years as a systems analyst on a Univac 1100/80, he joined HP in 1981. Mark developed

many of the compilers, Board Test BASIC statements and functions, and utility routines used in the software system for the HP 3065 Board Test System. A member of the ACM, he lives in Loveland, Colorado, where he recently bought his first home. Interested in almost anything athletic, Mark also enjoys occasionally reading a science fiction or fantasy novel.

#### 28 Short-Circuit Testing

#### T. Michael Hendricks

A graduate of the Massachusetts Institute of Technology (SB 1969, SM 1969, and EE 1972), Mike Hendricks worked on radar signal processing and medical data base systems before joining HP in 1980 as an R&D software engineer. His contributions to

the Shorts test for the HP 3065 Board Test System have resulted in one patent application. Mike was born in Baltimore, Maryland and is a member of the IEEE. Living in Loveland, Colorado, he enjoys running, swimming, ice skating, and acoustic guitar.

#### 31 Improved Analog Test Generator

#### John E. McDermid

A native of Twin Falls, Idaho, John McDermid joined HP in 1969 after receiving an MSEE degree from the University of Alberta at Calgary. He also holds a BSEE degree awarded in 1967 by the University of Idaho. The program manager for the

HP 3065 Board Test System, John also contributed to the HP 3490A Multimeter and the HP 3437A Digital Voltmeter and is the author of several papers on active filters and board test products. He is married, has a son and a daughter, and lives in Loveland, Colorado. Outside of work, John looks forward to fall when he can go bowhunting in the Rocky Mountains.

# **Automatic Test Program Generation for Digital Board Testing**

by Robert E. Balliew

EDUCING THE AMOUNT of time and the level of programming skill required to develop a valid test program is a highly desired feature of a printed circuit board test system. Using a "fill-in-the-blank" form of component and board data entry, the in-circuit program generator (IPG-II) of the HP 3065 Board Test System automatically creates a custom analog and digital test plan for a board, cutting test programming time for complex boards from weeks to a few days.

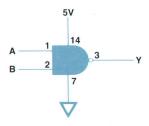

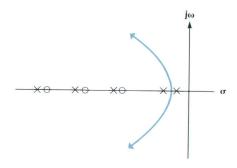

This article discusses the digital test generation methods used by IPG-II. The analog test generation methods are discussed separately in the articles on pages 28 and 31. The major tasks done by the digital portion of the program generator are scanner card pin assignment for digital nodes, modifying digital library tests affected by the board topology, and disabling other devices on the same bus with the device under test. Typically, IPG-II can write more than 90% of the tests for a circuit board without any user intervention other than data entry.

The program generator writes tests for each digital IC on the board. Each digital IC's test is kept in a separate file. The digital tests are compiled and a statement in the HP 3065's Board Test BASIC language causes a compiled digital test to be loaded into the test head and executed. The HP 3065 System contains a library of digital tests which the program generator uses to create the digital test for each IC on the board. (This library is discussed in the article on

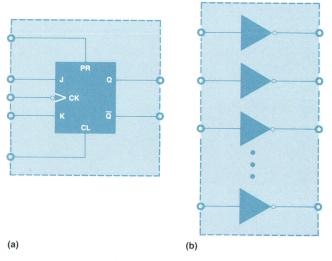

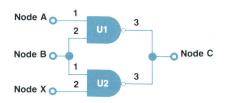

**Fig. 1.** (a) Example of a board topology that cannot be efficiently assigned for in-circuit testing. Here, seven channels and a multiplexing ratio of 1:1 are required. (b) Example of a board topology that can be efficiently assigned. Here, only two channels are required and the multiplexing ratio is 1:N, where N is the number of inverters on the board.

Fig. 2. Configurations of a NAND gate used as an inverter.

page 23.) To simplify the system for the user, the same language is used to write new tests for the library and/or for direct execution.

To reduce hardware costs, the digital stimulus/response channels in the HP 3065H Test Station are each multiplexed to a number of nodes on the circuit board under test (see article on page 14 and box on page 13). Obviously, the more nodes that can be multiplexed to one channel, the fewer the channels that are required for a given set of nodes and the lower the cost. However, there is a practical limit since each node of a single device under test must be assigned to a different channel. In addition, no node in the group of nodes assigned to a channel can require any of the other nodes in the group for any subsequent part of the board test sequence. In the HP 3065H, the multiplexing ratio is 1:4 and the task of assigning device nodes to channel groups is handled by the program generator so that there are no conflicts.

#### **Assignment Algorithm**

Before committing to a multiplexed digital hardware design, the feasibility of performing the desired test pin assignments had to be determined. Three things determine the efficiency of the pin assignment—the topology of the board (degree to which its ICs are interconnected), the assignment algorithm itself, and the multiplexing ratio. It is possible to postulate a board that cannot be efficiently assigned, namely a board with a single IC (see Fig. 1a). It is also possible to postulate a board that can be efficiently assigned, namely a board with N separate circuits (where N is greater than or equal to the degree of multiplexing, see Fig. 1b). All real boards must lie somewhere between these two extremes.

Fig. 3. Example of a bused part topology

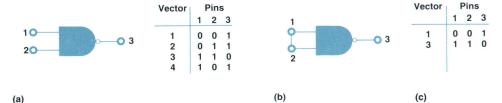

Fig. 4. (a) NAND gate and library test table. (b) Use of NAND gate in (a) on circuit board under test. (c) Modified library test for topology shown in (b).

An optimal assignment algorithm would be far too complex computationally, considering that a board could have in excess of one thousand nodes. The performance of an assignment algorithm is a function of how many different ways exist to assign the pins to the nodes without a conflict. To answer these design questions, two assignment routine variations were coded and run on over a dozen different real board topologies. Multiplexing ratios of 2:1, 4:1, 8:1, 16:1, and 32:1 were tried. The following general trends were observed in the data: all boards were assigned with good to very good efficiency (90% to 99%), the larger the board the more efficient the pin assignment, and the larger the multiplexing ratio the less efficient the assignment. Both variations of the assignment routine performed well. However, one had a slight advantage. One variation always attempted to assign pins so that existing channel groups were used fully. The other variation attempted to assign pins to channel groups in as balanced a fashion as possible. This second approach tended to leave openings in more groups, allowing more choices later in the process, which intuitively accounts for its slight efficiency advantage.

The assignment algorithm used by IPG-II consists of the following. First, the board topology is read in and then tests for each digital device are read from the HP 3065's device library. The program generator determines which test uses which nodes. The nodes are sorted in a manner that tends to make the pin assignment faster and more efficient. The program generator then loops through the list of nodes and looks for a pin location in the scanner to assign the node. If there are no tests in common between the tests required by the new node and the nodes already assigned to a multiplexed group, then the node is assigned to that group. Otherwise, the next group is checked. If no partially filled group is found in which a node can be assigned, then a new group is allocated. If upon completion more groups (channels) are allocated than the existing testhead hardware configuration can support, the user is informed of how many additional scanner pin cards are required. (The HP 3065 can contain up to 22 digital scanner cards, each providing 12 channels.)

#### **Real World Problems**

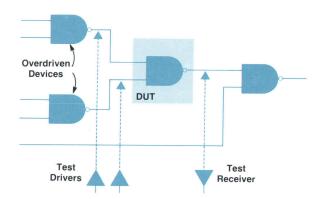

The basic concept of a digital in-circuit test system is to test each IC on the board as if it were a stand-alone part. However, since the ICs are actually installed on a printed circuit board, there are problems with simply testing the part as if it were a stand-alone IC. First, it is a common practice in digital design to change the function of a part by tying nodes together, tying a node high (logic one), or tying a node low (logic zero). For example, a NAND gate may be converted into an inverter by tying its inputs together or tying one input high (see Fig. 2). Another problem induced by having the IC installed on a board is that some of the ICs may be bused together (see Fig. 3). To observe the response of one device on a bus, all other devices on that bus must be disabled.

IPG-II has the intelligence to handle testing problems that might be encountered because of the above constraints. This reduces the effort required to write a new test for the library because the library test programmer need not be concerned with anticipating and handling all the possible various alternate topologies for a device. Instead, the programmer concentrates on writing a test that does a good job of testing the part and the program generator takes care of adapting the test for alternate topologies. For devices that can be disabled, all that is required in the device test library is the information on how to disable the device.

Digital test generation involves analyzing the board topology around each digital part on the board. Based on this analysis, the standard library program for each device is automatically modified by IPG-II to resolve conflicts between the topology and the library program and to disable other devices bused to the device under test. The topologies for which the program generator must modify the library test are nodes tied high, low, or unknown, unconnected nodes, and nodes tied together.

#### **Resolving Topology Conflicts**

All nodes that are tied high, tied low, tied unknown, and unconnected in the topology have their pin numbers replaced by a \* in all assign statements in the digital library

**Fig. 5.** (a) D-type flip-flop and library test sequence. (b) Use of flip-flop on board under test. For this topology, the library test is modified by removing test vector unit one.

Fig. 6. (a) Open-collector output NAND gate. (b) Library test and disable vectors for (a).

program. The \* pins are ignored when the test is compiled. This technique allows the program generator to handle nodes that are tied high, low, or unknown, or that are unconnected without requiring it to modify and reformat all the vector definition blocks in a test program.

The program generator looks at the test, checking each test vector separately for conflicts with the topology. If any pin setting is in conflict with the topology, then the vector containing it is in conflict, and the program generator will not allow the vector to be executed. If the test is a combinatorial digital program, then conflicting execute, preset counter, count, or call statements are deleted. If the library test is a sequential digital program, then the entire digital unit in the program (unit through end unit statements) containing a conflicting vector is removed.

To show how the program generator handles a typical test situation, suppose that the library contains a test for a NAND gate as shown in Fig. 4a. The board under test uses this part as shown in Fig. 4b. Hence, IPG-II modifies the library test by removing the execute commands for vectors two and four, resulting in the test shown in Fig. 4c.

Obviously the program generator cannot simply remove only the conflicting vectors from the test for a sequential device and still expect the test to work properly. To handle this situation, sequential tests are organized into units that are independent of each other. Each unit contains one or more vectors as shown in Fig. 5a, which lists a portion of the library test for a D-type flip-flop. As an example, consider the case where this device is connected as shown in Fig. 5b. Since this device test is sequential and the first vector in unit one is in conflict, IPG-II modifies the library test for this topology by removing unit one.

#### **Disabling Buses**

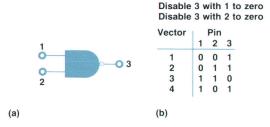

To test a device, all outputs of other devices bused to the device under test must be disabled so that the response of the device under test can be observed. The program generator disables devices by using one vector executed one or more times, depending on the devices involved

Fig. 7. Bused arrangement of two of the parts shown in Fig. 6.

## **Board Test Connection Terminology**

The reader not intimately familiar with board testing may find the nomenclature used to describe circuit and test system electrical connections to be occasionally confusing. For example, the term "pin" can be used to describe a lead of an IC, the spring-loaded pin in the "bed-of-nails" test fixture, or an input/out-put connection on a digital scanner card. Hence, the figure below may be a useful reference.

(some may have to be clocked), and then left set for the duration of the device test. If the program generator cannot find a way to disable all the buses simultaneously without affecting any of the nodes of the device under test, it checks all the vectors remaining in the test for conflicts with the enabled device. If there is a conflict, the program generator asks the user to add the code to disable the buses manually. IPG-II will disable as much of each bus as it can.

For example, suppose that the device shown in Fig. 6a has a test in the library as shown in Fig. 6b. Fig. 7 shows two of these devices connected in a bus arrangement. When testing U1, the program generator must determine how to disable U2 without affecting the test for U1 and then modify the test for U1 so that it performs the disable vector. Fig. 8 shows the modified test. Note that the program generator can not use node B in Fig. 7 to disable U2, because that node is required by the test for U1.

IPG-II disables buses on a device by adding the nodes required to disable the buses to the device's test program. These nodes are specified in assign statements added to the declaration section of the device's test program. The value

| Vector  | Node |   |   |   |  |  |  |

|---------|------|---|---|---|--|--|--|

|         | Α    | В | C | X |  |  |  |

| Disable |      | - | _ | 0 |  |  |  |

| 1       | 0    | 0 | 1 | 0 |  |  |  |

| 2       | 0    | 1 | 1 | 0 |  |  |  |

| 3       | 1    | 1 | 0 | 0 |  |  |  |

| 4       | 1    | 0 | 1 | 0 |  |  |  |

**Fig. 8.** Executable test for U1 in Fig. 7 showing inclusion of the disable vector for U2.

required for each node is specified in each node's assign statement. All nodes required to disable the buses are assigned to a set of pins named Disablegroup. The program generator also adds an input statement that specifies Disablegroup to the device's test program.

After all digital units and vectors that conflict with the topology around the device have been removed, the disable vector is placed above the first digital unit. The execute vector statements (or a repeat loop and an execute vector statement) are placed inside of a new unit. The execute statements refer to a vector called Disablevector which has no defining vector block. Disablevector is created by the compiler to set all the pins to their default settings. Disablevector may be executed several times before the test starts. The number of times it is executed is determined by the disable statements from which Disablevector was constructed.

#### **Modifying Library Tests**

IPG-II forms the executable digital test from the library source. This minimizes the number of machine-generated statements the source contains. Since it is possible for some of the tests to require some manual modification after the program generator has run, the more readable the test, the easier the modifications. The program generator puts comments in the test programs it generates to help the user. Most of the comments start with ! IPG: to help flag them as comments placed into the source by the program generator.

One comment documents which revision of the software created the test and what day and time the source file was created. Another comment informs the user which devices and nodes must be disabled before a device can be tested. In most cases, the program generator will not list every device and node that was not disabled but will list the key devices and nodes that, if disabled, will assure that no device bused to the device under test is enabled (this is because of a common enable for many outputs). If IPG-II removes a unit from a device test, it generates a comment informing the user that a unit was removed from the test. Whenever IPG-II finds a conflict between the topology around a device and a vector, it generates a comment informing the user of the conflict. If a test unit was removed because of this conflict, the conflict comment appears right below the removed unit comment; otherwise, it appears at the location of the removed vector's execute, preset, count, or call statements. The comment shows the name of the vector and the pin name or node name that has the conflict. Pin names are shown in cases where the conflict is with a node tied high, low, or unknown, or unconnected. Node names are shown if pins tied together are in conflict. The comment also indicates the reason for the conflict-conflict with pin tied high, conflict with pin tied low, conflict with pin tied to an unknown value, conflict with an unconnected pin, and conflict between pins tied together.

#### **Acknowledgments**

Tom Fay provided the library access routines and many helpful suggestions about testing and structuring the HP 3065's in-circuit test program generator. Bill Groves, who helped in the definition of IPG-II, developed the pin assignment algorithm and provided much insight about algorithm design and efficiency.

Rod Browen coded the analog portion of IPG-II, including writing of the test plan and the Shorts test.

## Digital Subsystem for a Board Test System

by Matthew L. Snook and Michael A. Teska

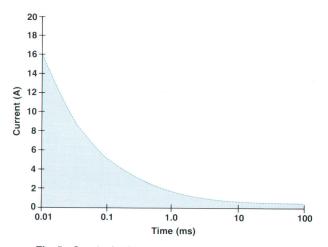

N ANY PRODUCT DEFINITION, it seems that a major issue is how to divide features into software and hardware implementations. However, often certain product features can only be realized in hardware because of their very nature. The digital hardware subsystem for the HP 3065H Test Station of the HP 3065 Board Test System was designed to address universal test needs in the areas of fault coverage, cost, performance, ease of operation, and throughput in addition to a multitude of specific digital in-circuit test needs. These needs include long complex pattern sets, a high pattern rate to meet the minimum clock rate required by dynamic devices, short test duration to

minimize the potential for damage to overdriven devices, high throughput to minimize testing costs, and a set of test vectors known as a homing sequence to initialize some sequential devices to a known state before testing.

A traditional architecture approach might have addressed most of these goals by simply using more high-speed RAM behind the test pins to store a greater number of test vectors. However, this leads to higher costs and to lower system throughput because of the large amount of test pattern data to be downloaded, which is by far the controlling factor in determining throughput. The HP 3065H architecture uses one local high-speed control card

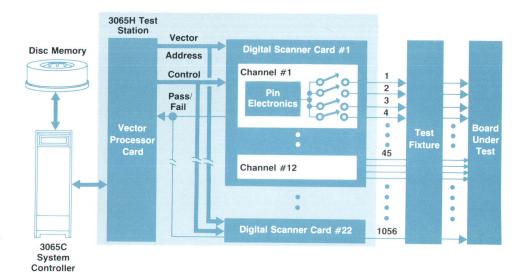

**Fig. 1.** Architecture of the HP 3065 Board Test System.

to sequence the proper execution of test vectors residing on several digital scanner cards, each containing RAMbacked digital drivers and receivers.

#### **Board Test System Overview**

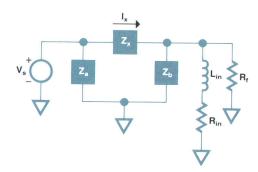

The basic architecture for the HP 3065 Board Test System is shown in block diagram form in Fig. 1. The HP 3065C System Controller runs the board test program that sequentially tests each device on the circuit board under test. Within the HP 3065H Test Station is a single high-speed control card, called the vector processor card, and several digital scanner cards. Each driver/receiver channel is multiplexed through relays and wiring to four spring-loaded test pins in the "bed-of-nails" test fixture designed for the board under test (see cover photograph). A vacuum in the test fixture assembly pulls the board under test down to connect its circuit nodes to the spring-loaded pins. There are twelve channels per digital card and up to 22 of these cards can be installed in the HP 3065H, resulting in up to 264 channels multiplexed to 1056 nodes on the board under test.

By placing a great deal of emphasis on the capabilities of the high-speed control card, the HP 3065 Board Test System was designed to perform long complex pattern sets of both an algorithmic and manual nature, do real-time pass/fail checking off-line from the host system controller, provide pattern rates up to 2.5 MHz, and much more. Throughput limitations imposed by the time required for memory accesses are eased by downloading only a small amount of information and allowing the high-speed control card to create the long complex patterns programmatically.

The HP 3065C Controller downloads all of the test pattern data for a specific device test from disc memory to the vector processor card and digital cards. This data includes the vector data for the pin RAM on the digital cards, the sequence program for the program RAM on the vector processor card, and other specific test parameters to be set up on various cards. The vector processor card then takes over control and locally executes the program to test the device, giving pass or fail results to the controller when finished. This allows the controller to perform other tasks during

test execution, which increases system throughput.

To execute a particular vector, the vector processor card issues the proper vector address to all pin RAMs, accesses the test vector data consisting of drive data and expected response data, clocks the vector data, waits a programmable receive delay time, samples the response data, and then examines the pass/fail result indicating whether all of the responses were correct or not.

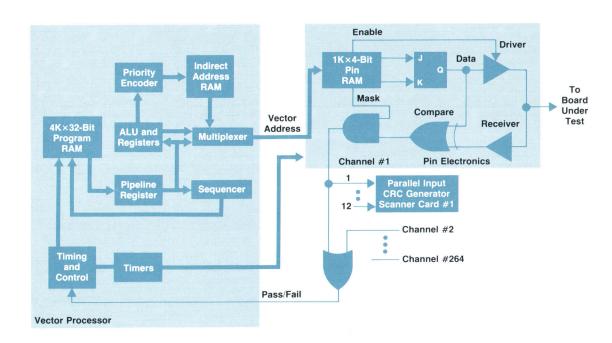

#### **Digital Subsystem Architecture**

Fig. 2 shows an expanded view of the digital subsystem architecture with a more detailed block diagram of the vector processor and digital scanner cards. The vector processor consists of a  $4K \times 32$ -bit RAM with 32-bit instruction words which are addressed by the sequencer and clocked into the pipeline register for execution. The sequencer controls execution of program flow by doing conditional and unconditional branches. The ALU (arithmetic logic unit) and registers are used for repeat loops, parameters for subroutines, and algorithmic counter generation. The priority encoder and indirect address RAM are used for algorithmic counter generation as explained later. The multiplexer selects one of three sources to be used as the vector address depending on whether the vector is a simple vector, a parameter vector, or an algorithmic counter vector. The timing and control block consists of a two-phase 10-MHz clock circuit and an algorithmic state machine that control the entire vector processor card program flow. The timers measure the programmable time relationships of the clock and control signals sent to the digital scanner cards.

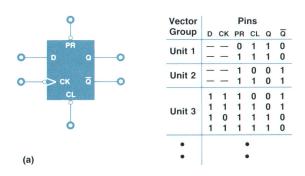

After a vector address is issued to the digital cards, the vector data is accessed from the 1K×4-bit test pin RAM and clocked into a J-K flip-flop. The two bits clocked into the J-K flip-flop can indicate one of four possibilities: 0, 1, keep (K), or toggle (T). Keep means that the next state is the same as the present state and toggle means that the next state is the opposite of the present state. The state of the J-K flip-flop indicates the expected response or the drive state that the driver will drive. The third bit in the pin RAM is for driver enable to turn the driver output on or off (high impedance). The last bit is the mask bit used

### **Digital Test Throughput**

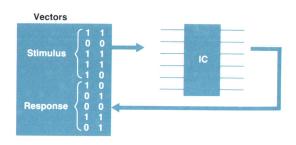

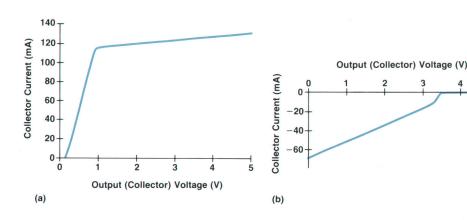

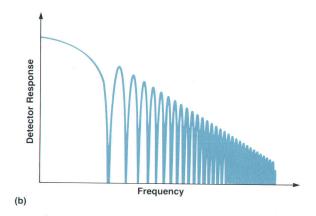

Testing digital devices on a system such as the HP 3065 Board Test System involves applying a set of digital stimulus signals to the device to be tested and verifying that the digital responses generated by the device are correct. A typical test involves a sequence of these stimulus/response patterns, called vectors, to test for a variety of manufacturing defects that might affect the correct operation of the device on a printed circuit board (Fig. 1).

The trend, as devices become larger and more complex, is for the corresponding tests to grow similarly. This means that tests involve more pins (increased vector width) and more vectors (increased vector depth). In addition, users frequently wish to add functional subtests to the device tests, again resulting in larger digital tests.

Test size can be viewed as the product of the width of the vectors (the number of device inputs and outputs) and the number of vectors in the test. For a typical TTL part, this doesn't look too alarming—16 pins times 200 vectors requires 3200 bits of information to specify the test. However, as devices get larger, the amount of information gets quickly out of control—64 pins times 2000 vectors requires 128,000 bits of information. The problem is compounded by the fact that there are increasing numbers of such devices on a typical circuit board, and each device must have its own test. All of this information must be created, stored, retrieved, and transferred to the test-head electronics as part of the generation and execution of digital tests.

The HP 3065 addresses this potential testing bottleneck with a combination of hardware and software features. One goal of the hardware design for the HP 3065 was to reduce the amount

of information needed to generate the vectors making up the test. The design was guided by a number of observations. The first observation is that the vectors applied to the device under test generally involve a fair amount of redundancy. The same vector pattern is frequently used in various portions of the test. The same sequence of vectors, with possibly a few vector differences, is also repeated frequently within the same test. The HP 3065 takes advantage of this by separating the storage of the vectors from the sequence of execution information. Unique vectors are stored in vector RAMs, and a special processor, the vector processor, controls the sequence of application of these vectors to the device. This processor permits repeat loops, subroutines with parameters, and repeated use of the same vector.

A second observation is that the vectors themselves often have a great deal of similarity. The HP 3065 takes advantage of this by permitting vectors to be specified in terms of the changes (toggles) or nonchanges (keeps) from the last vector executed (Fig. 2). As an important special case, vectors are often the same except for a particular subset of the pins that have a count associated with them-address pins are a typical case. For this case, the HP 3065 has the capability of generating these "count" vectors algorithmically, with the result that literally thousands of vectors can be generated using very compact tests. This count capability is particularly powerful when coupled with the ability of the HP 3065 to calculate a cyclic redundancy code (CRC) checksum for the device outputs over all the vectors applied to the device under test. Using this capability, extremely compact tests can be created for ROMs by using the count feature to generate addresses and the CRC capability to specify the ex-

**Fig. 2.** Digital subsystem architecture of the HP 3065H Test Station (see Fig. 1) Although only the pin electronics block diagram for one test channel is shown, there are 12 channels on each digital scanner card and the HP 3065H can accommodate up to 22 cards or 264 channels.

**Fig. 1.** Digital in-circuit testing is defined by vectors that describe the input test pattern and the expected response pattern for a device.

| Unique<br>Vectors | + | Test<br>Sequence | = | Test<br>Patterns |

|-------------------|---|------------------|---|------------------|

| 1: 0000           |   | 1                |   | 0000             |

| 2: TTKK           |   | 2                |   | 1100             |

| 3: KTKT           |   | 3                |   | 1001             |

|                   |   | 2                |   | 0101             |

|                   |   | 3                |   | 0000             |

|                   |   | 1                |   | 0000             |

|                   |   | 3                |   | 0101             |

|                   |   | 2                |   | 1001             |

|                   |   |                  |   |                  |

**Fig. 2.** By using keep and toggle descriptions, the number of vectors required to describe a long set of digital test patterns can be greatly reduced, increasing test throughput and reducing data storage size. In the above example, three unique keep/toggle vectors can be used to form a test sequence of eight test patterns.

pected ROM data contents concisely.

Even with the advanced architecture of the HP 3065 hardware, the amount of data associated with testing the digital parts on a board can be significant. The primary bottleneck associated with digital testing is still getting each test from the system controller's

disc memory to the test hardware. For this reason the HP 3065's software is specially designed to enhance speed through this bottleneck by tuning the software and data organization to support the normal way that digital testing is done for a printed circuit board. The key is that the typical board test will test all devices in a specific sequence that does not vary. To take advantage of this, digital tests are stored in a specially organized file called the turbofile. This file is built to occupy contiguous blocks of the disc and contains the tests in the order that the board test will need them. The software to execute the digital tests uses a large buffer in memory for reading in the tests so that as testing proceeds each disc access reads in a number of digital tests. By doing this, disc access overhead can be shared over a number of tests, reducing dramatically the overhead per test caused by disc accessing. The advanced hardware architecture permits compact tests that make this scheme feasible. As an example, a disc access might take 40 milliseconds on the average. Because of the HP 3065's software structure, a block of 20 tests can be read during one access, resulting in 2 milliseconds of overhead associated with each test instead of 40 milliseconds of overhead per test if each test were read from the disc individually. A second part of tuning the software for increased throughput is to make maximum use of the DMA interface between the system controller and the test-head electronics. Tests in the turbofile are set up to require no processing at run time before invoking the DMA transfer from the controller to the test head, and these tests are further designed to perform relay closure operations that require settling delays at the beginning of the DMA operation. This overlaps the downloading of the test's data with the delay required for the relays to settle. Thus, a typical digital test gets loaded into the test head while relays are closing and the download time is typically masked entirely by relay closure time.

#### Acknowledgments

Vance Harwood and Bill Groves provided the leadership that resulted in the software that makes the HP 3065 go.

Thomas R. Fay Project Manager Manufacturing Test Division

when the response is not to be tested. Therefore, there are nine basic states that the vector data can indicate: drive 0, drive 1, drive keep, drive toggle, receive 0, receive 1, receive keep, receive toggle, and X (don't care—receiver masked and driver off). The concept of keep/toggle vectors is a key feature in being able to generate a large number of test patterns from a small amount of downloaded data (see box on page 16).

All channels used for a single device test (up to 264) have their compared responses ORed together to create a single pass/fail line which is monitored in real-time by the vector processor card after each vector. This pass/fail result can indicate a truly failing vector, or can be used as a test condition for a conditional jump statement at the end of a homing sequence loop (e.g., "jump" out of the loop if "passed").

Each digital scanner card also has all twelve channels of compared response fed into a parallel input cyclic redundancy check (CRC) generator on that card. The CRC generators on all cards are simultaneously clocked with input data on selected vectors until the test is complete

and a signature is generated from the bit stream. Thus, all outputs of a device can be captured with only one application of the test stimulus which, for example, is an ideal way to verify the contents of a large ROM.

The design of the vector processor card includes features that help execution speed such as one level of pipelining instructions, two-phase 10-MHz clocks to allow two sets of circuitry to communicate with each other at a high rate, the prefetch of instructions and execution when possible, a special algorithmic state machine that executes each instruction as quickly as possible (rather than all at the rate of the slowest one), and a minimal instruction set customized for this application. By using generous portions of conventional high-speed RAM and bit-slice processor components, these features were achieved without the need for custom devices.

The vector processor card supports other vector sequencing hardware features that include subroutines with up to 16 vector addresses passed as parameters, repeat loops up to a count of 65,536 times with up to 16 levels of nesting, and algorithmic counter generation of up to sixteen simul-

taneous 16-bit counter fields.

The fact that the vector data is stored in the test pin RAM and is accessed by sending a vector address from the vector processor card means that the same vector may be accessed repeatedly during a test. This reduces the number of vectors that have to be stored for a test and thereby reduces the amount of data to be downloaded for a test, which increases throughput.

#### **Keep/Toggle Vectors**

Keep/toggle vectors allow the next state of a test pin to be determined by the current state. It can be observed that for a set of N-bit-wide patterns in which only one bit changes between successive patterns, there exists a set of only N unique keep/toggle vectors that can be used to describe any such change. For example, an 8-bit Gray code counter in which only one bit changes between successive patterns would then require only eight unique keep/toggle vectors in which only one bit toggles for each new vector and the rest are kept the same. See box on pages 16 and 17 for another example.

This simple but effective concept is used by the hardware to create a counting sequence up to N bits wide algorithmically on any set of test pins by simply accessing the N unique vectors in the proper sequence. The reduction in downloaded data is substantial since the creation of an N-bit counter that can count through 2<sup>N</sup> states requires only N unique keep/toggle vectors plus one initialization vector. In the HP 3065H Test Station, N is a maximum of 16. Hence, 65,536 test patterns can be created from only 16 keep/toggle vectors. Other algorithmic counter sequences are also implemented just as simply by using a different set of unique keep/toggle vectors, including a binary up-counter and down-counter.

An example of the dramatic data reduction is the library test for a  $2K \times 8$  PROM that tests all 16,384 bits of the PROM by algorithmically generating 2048 test patterns from only 12 unique downloaded vectors, resulting in a downloaded data reduction of 171 to 1.

The beauty of this architecture is that the same pin electronics hardware and relay multiplexing are used for all of these features. Any test channel can be bidirectional on the fly, can change at the maximum pattern rate, can be an algorithmic counter pin or simple vector pin, etc.

#### **Digital Scanner Card**

Digital signal quality was one of the primary design con-

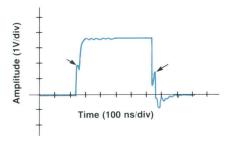

**Fig. 3.** Digital test stimulus waveform with glitches (indicated by arrows). If not eliminated or reduced, these glitches can cause erroneous test results.

siderations in the design of the digital scanner card. At issue is the quality or fidelity of the signals at the device under test (DUT), and hence, the quality of the test.

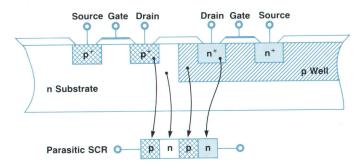

Before we get into details on the methods to achieve good signal quality, let's first examine what will happen with poor signal quality. Some of the possible testing problems caused by poor signal quality are:

- Double clocking

- CMOS latch-up

- Oscillations

- Nonrepeatable tests.

These testing problems are caused primarily by glitches, voltage overshoot and undershoot, and slow edge speeds (rise and fall times) in the stimulus applied to the DUT.

Glitches are the most prevalent and most difficult problem to solve (see Fig. 3). They can be responsible for the double clocking of a circuit (a counter, for example), causing the test to fail. Glitches can also lead to unrepeatable tests when they are caused by other events during the board test that may not occur each time the test is run (for example, homing loops may be executed a different number of times depending on how the board powers up). These glitches may appear on control lines and cause a part to reset or perform other unintended operations.

Glitches can be caused by crosstalk in the test fixture or in the test system if proper care is not taken in the test system design or the test fixture wiring. They can also be caused by capacitive terminations at the end of a transmission line (which the test fixture contains, regardless of the wiring scheme used).

Overshoot and undershoot occur when a transmission line (the wires in the test fixture) is terminated with an impedance greater than the characteristic impedance of the line. (This is very common when testing CMOS, whose impedance is typically about  $500\Omega$ ). The size of the overshoot and undershoot increases with the edge speed (rise and fall times) of the source (in this case, the board test system). Of course, overshoot and undershoot can also be caused by poorly designed pin scanning electronics.

Very slow edges at the DUT can cause the DUT to oscillate. This occurs because the input of the DUT is held in its switching region (for TTL, between 0.8V and 2.4V) for a long enough time to let noise on the input (from the output switching) cause the device to oscillate. If the impedance of the source driving the input is sufficiently high, the noise may be so severe that even when the source reaches its steady-state value, the input may still be moving through the switching region, causing the oscillations to continue. As before, the design of the pin scanning electronics also influences the edge speed of the test stimulus.